SPI Demystified: Understanding the Basics and Beyond

Published

Introduction

Serial Peripheral Interface is one of the most common communication protocols microcontrollers use to communicate with peripherals such as SRAM, SD cards, shift registers, sensors, etc. It is a synchronous, full-duplex, master-slave-based protocol. It supports high-speed data transfer, and there is a direct relationship between the data speed (bps) and the clock frequency (Hz) in SPI protocol. For example, if the clock frequency of the SPI is 36 MHz, the transfer speed will be 36 Mbps. Hence, there is no limit on the transfer speed of the SPI protocol. It solely depends upon the clock frequency supported by the device. Talking about the connections, SPI is a 4-wire interface with the following signal lines:

- Master Out Slave In (MOSI)

- Master In Slave Out (MISO)

- Clock (SCLK)

- Slave Select

SPI Interface

MISO and MOSI are the primary data lines to transfer the data. SCLK is the clock signal generated by the master to sample the data on the bus. Finally,

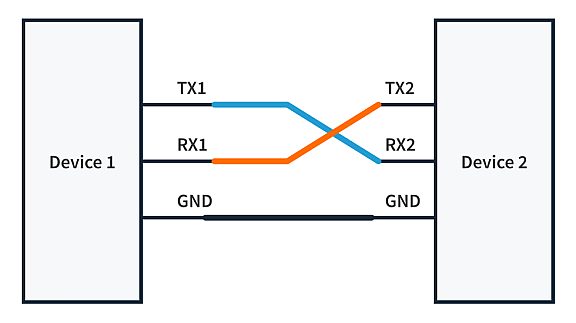

Connecting devices using SPI is straightforward and clear. Each pin on the master connects to the same pin on the slave, leaving no room for confusion. The master's MOSI connects to the MOSI of the slave, and the master's MISO connects to the MISO of the slave. And the same goes for SCLK and

SPI Data Transmission

As mentioned earlier, SPI is a full duplex communication, meaning the master and slave can transmit and receive simultaneously with their respective MOSI and MISO lines. One of the major advantages of SPI is that there is no need for start and stop bits because the SCLK line of the bus synchronizes the data. The SCLK line synchronizes the shifting and sampling of the bits on the data lines, which is explained in detail in the later part of the article.

Regarding the number of bits that can be transferred, the supported word length for SPI protocol ranges from 3-16 bits, but the standard is 8 bits. If the master and slave want to share 2 bytes at once, they can choose a word length of 16 bits and utilize a 16-bit data register (if available on the MCU) or transfer it in a chunk of two 8-bit data packets.

SPI also supports multiple slaves connected to the same master. For each slave, there has to be a separate SS line. The data exchange occurs only between the master and the selected slave; the remaining slaves on the bus remain inactive and cannot use their MOSI and MISO lines. Figure 2 shows the connections for multiple slave setups.

But everything isn’t perfect with SPI. When it comes to the SS lines, they are simply digital I/O pins. Hence, the number of slaves that can be connected is limited by the available I/O pins on the microcontroller.

Why use a clock with SPI?

The question may arise: why introduce a clock line if the serial protocol can work asynchronously just fine? If you’ve read our tutorial on UART, you know that the devices communicating via UART do not have a common clock to synchronize the data transfer between them. The communicating devices rely on their internal clocks for the sampling of data. Hence, the clocks need to be precise, or else garbage data is received. Moreover, extra bits are used to mark the start and end of the data frame, which causes a lot of overhead for large transfers. But when it comes to SPI, it eliminates the need to mark the start and end of the data frames and synchronizes the data on the rising or falling edges of the clock signal. Let’s take a look at how SPI achieves this.

Before we move forward, we’ll explain two important terminologies that will be used in the next section of the tutorial:

SPI Clock Modes with CPOL and CPHA

SPI Mode | CPOL | CPHA | Clock Polarity in Idle State | SCLK Edge | |

|---|---|---|---|---|---|

Bit sample | Bit shift | ||||

0 | 0 | 0 | Logic Low | Rising | Falling |

1 | 0 | 1 | Logic Low | Falling | Rising |

2 | 1 | 0 | Logic High | Falling | Rising |

3 | 1 | 1 | Logic High | Rising | Falling |

Table 1: Clock Modes sampling and shifting

1. SPI Mode 0 - CPOL : 0, CPHA : 0

Data is sampled on the rising edge and shifted out on the falling edge of the clock signal. Here, the clock polarity is low in the ideal state; when no data is being transferred, the clock line is low.

2. SPI Mode 1 - CPOL : 0, CPHA : 1

Data is sampled on the falling edge and shifted out on the rising edge. Here, the clock polarity is similar to the previous case (mode-0); the clock line is low in the ideal state when no data is being transferred.

3. SPI Mode 2 - CPOL : 1, CPHA : 0

Data is sampled on the rising edge and shifted out on the falling edge of the clock. Here, the clock polarity is high in the ideal state.

4. SPI Mode 3 - CPOL : 1, CPHA : 1

Data is sampled on the falling edge and shifted out on the rising edge of the clock. The clock polarity is similar to SPI Mode - 3, high in the ideal state.

An embedded engineer must know the SPI clock modes because the slave devices usually come pre-configured with one of these modes. You can locate the clock operating mode for the slave in its respective datasheet. Once we identify the operating mode for the slave, the master can be configured accordingly to communicate with the slave over the SPI bus.

Data reception and transmission in registers of SPI

Microcontrollers supporting SPI protocol have a dedicated set of control and data registers. These special-purpose registers configure clock modes (as we saw above) and transmit and receive data between the communicating devices.

SPI follows the SISO (Serial In, Serial Out) method - a new bit is received for every bit sent. So, on each clock pulse, one bit from the master’s data register is transmitted to the slave’s data register via the MOSI line, and at the same time, one bit from the slave’s data register is transferred back to the master’s data register via the MISO line

This process of data transmission and reception is shown visually as follows. We’ve considered the clock control bits as CPHA = 0 & CPOL = 0:

1. Data is stored in the respective SPI data registers of both master & slave.

2. To begin the communication, the master sends the clock signal and selects any one of the connected slaves by enabling the

3. Both the master and slave sample the LSB on the rising edge (CPHA = 1) of the SCLK line and store it in the MSB of their data registers.

4. Now, the following bits of the data registers are shifted out on the falling edge of the clock pulse, clearing the MSB to read the next bit, and the new LSB is shifted out on the data lines. And again, on the rising edge, the next bits are sampled and stored in the registers.

5. This process is repeated on every clock pulse until all the 8 bits on the registers are transferred from master to slave. Hence, the data is sent byte-by-byte from the master to the slave and vice-versa. After completion of the data transfer, the master ends the communication by disabling the

Daisy Chain Method in SPI

In the SPI configuration we discussed above, slaves require individual lines to communicate with the master, but there could be cases when the number of available digital pins to use as

SPI Interface

In the Daisy Chain method, the

The MOSI of the master is connected to the MOSI of slave 1, but this time, the MISO of slave 1 is connected to the MOSI of slave 2, and the MISO of slave 2 is connected back to the MISO of the master. This can be confusing to understand, so the diagram below should help.

Similarly, if you have a setup with N slaves in the daisy chain configuration, again, the MOSI of the master is connected to the MOSI of slave 1 and the MISO of slave 1 is connected to the MOSI of slave 2. Similarly, the MISO of slave 2 is connected to the MOSI of slave 3, and so on until the Nth slave. Finally, the MISO of the Nth slave is connected back to the MISO of the master.

SPI Data Transfer

To understand the data transfer in the daisy chain configuration, let’s consider the same configuration as shown in Figure 5 above. The master wants to send packet-1 and packet-2 to slave-1 and slave-2, respectively. The packet transfer in daisy chain configuration will be carried out in the following way:

1. To initiate the communication, the master will enable the SS line by pulling it low, waking up both the slaves.

2. Master will then send out packet-2 to slave-1, which will be stored in slave-1’s buffer.

3. As per the standard SPI protocol, the packet size is 8 bits. Hence, after exactly 8 clock cycles, slave-1 will start sending packet-2 to slave-2 via the MISO-MOSI connection and simultaneously receive packet-1 from the master.

4. Once both the packets reach their desired destination, slave-2 notifies the master by sending a response byte via the MISO-MISO connection between them. After receiving the response byte, the master ends the communication by disabling the SS line on the SPI bus.

Using a Daisy Chain configuration reduces the requirement for multiple I/O pins required for 𝑆𝑆 lines. However, it also results in a delay in data transfer as the number of slaves increases. When implementing the Daisy Chain method, ensuring that all chips use the same clock edge and idle clock state is crucial. If the devices do not use the same clock conditions, you can expect unreliable communication, data corruption, or complete failure to exchange data between devices.

Conclusion

The SPI communication protocol is excellent for communicating with SD card modules, various sensors, and industrial testing with powerful diagnostic tools. It offers benefits such as high speed, simplicity, and low cost but also has drawbacks such as limited range and requiring more pins than other communication protocols.

Get the latest tools and tutorials, fresh from the toaster.